2024年电子行业报告:先进封装趋势与国产机遇分析

1.先进封装提升芯片性能,Bump、RDL、TSV等技术赋能AP

1.1封装是半导体后道制程,主要起芯片保护、连接作用

半导体封装主要有机械保护、电气连接、机械连接和散热四大功能。半导体产业链可以分为IC设计、晶圆制造(前道工艺)、封装测试(后道工艺)三个核心环节。半导体封装,指用特定材料、工艺技术将芯片密封在塑料、金属或陶瓷等材料制成的封装体内,从而保护芯片免受物理性和化学性损坏。通过封装,还可以使芯片能够与其他电子元件进行连接,实现信息的输入输出。半导体封装主要有机械保护、电气连接、机械连接和散热四大功能。芯片封装完成后,需要进行性能测试,以确保封装的芯片符合性能要求。

集成电路封装技术的发展可分为四个阶段。第一阶段是20世纪70年代开始应用的通孔插装技术;第二阶段是20世纪80年代的贴片式封装技术;第三阶段是20世纪90年代开始应用的BGA、WLP、CSP技术;第四阶段是20世纪末开始的MCM、SIP、3D堆叠、Bumping等;第五阶段是20世纪前10年开始应用的SoC、MEMS、TSV、FC、SAB、Fan-Out、Fan-in等技术。

1.2Bump、RDL、TSV、混合键合技术赋能先进封装

先进封装(AdvancedPackaging,AP)也称为高密度封装,通过缩短I/O间距和互联长度,提高I/O密度,进而实现芯片性能的提升。相比传统封装,先进封装拥有更高的内存带宽、能耗比、性能,更薄的芯片厚度,可以实现多芯片、异质集成、芯片之间高速互联。Bump、RDL、TSV、HybridBonding等是实现先进封装的关键技术。

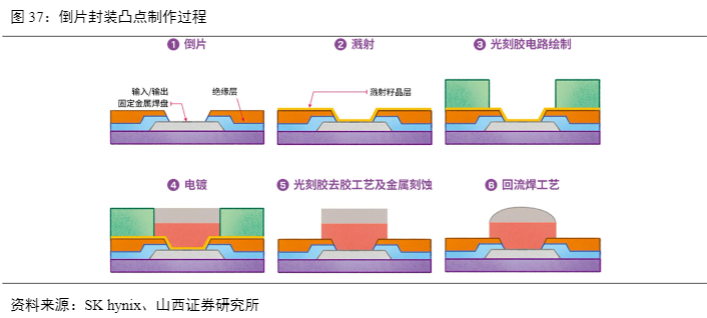

凸块(Bump)

传统封装的电路连接主要依赖引线框架,先进封装的电路连接则主要通过凸块完成。通过在芯片表面制作金属凸块,提供芯片电气互连的“点”接口,反应了先进制程以“以点代线”的发展趋势。Bump技术以几何倍数提高了单颗芯片引脚数的物理上限,进而大幅提高了芯片封装的集成度、缩小了模组体积,广泛应用于WLP、CSP、2.5D/3D等先进封装。随着工艺技术的发展,Bump的尺寸和间距也变得越来越小。

重布线层(RedistributionLayer,RDL)

RDL是在晶圆表面沉积金属层和介质层并形成相应的金属布线图形,来对芯片的I/O端口进行重新布局,将其布置到新的、节距占位可更为宽松的区域,其主要作用是XY平面电气延伸和互联。RDL去除了昂贵且耗时的键合工艺,同时可以大幅提高I/O密度,改善电气性能和减少芯片面积。

RDL广泛应用于FIWLP、FOWLP、2.5D/3D等先进封装。(1)FIWLP、FOWLP封装,RDL将IOPad进行扇入或者扇出,形成不同类型的晶圆级封装。(2)2.5D封装,RDL将网络互联并分布到不同的位置,从而将硅基板上方芯片的Bump和基板下方的Bump连接。(3)3D封装,如果堆叠上下是不同类型的芯片,需要通过RDL将上下层芯片的IO进行对准,从而完成电气互联。

TSV是一种垂直互连技术。国际半导体技术路线蓝图将TSV定义为连接硅晶圆两面并与硅衬底和其他通孔绝缘的电互连结构。相比平面互连,TSV可以减小互连长度和信号延迟,降低寄生电容和电感,实现芯片间的低功耗和高速通信,增加宽带、提高集成度、实现封装小型化。TSV按照集成类型的不同分为2.5DTSV和3DTSV。2.5DTSV指位于硅转接板Inteposer上的TSV;3DTSV指贯穿芯片体之中,连接上下层芯片的TSV。

混合键合(HybridBonding,HB)

混合键合是对Bump技术的进一步升级。Bump技术中,当接触间距减小到10μm左右时,凸点尺寸的减小会增加金属间化合物(IMC)形成的风险,从而降低导电性和机械性能。混合键合又称为直接键合互连(DirectBondInterconnect,DBI),通过两个芯片覆盖介电材料如二氧化矽(SiO2),介电材料嵌入与芯片相连的铜接点,接着将两芯片接点面对合,再进行热处理让两芯片铜接点受热膨胀对接。混合键合最大的特点是无凸块,它从基于焊料的凸块技术转向直接铜对铜连接。

混合键合可以提供更高的互连密度和键合可靠性。(1)相较Bump技术,混合键合最大优势是缩小接点间距,Bump键合最小接点间距约10μm,混合键合能缩小至1μm甚至更低。(2)芯片更小接点间距意味相同尺寸,混合键合能做出更多I/O接点,甚至能在1cm²芯片做出百万个I/O接点,相较传统覆晶焊锡接合,接点数能提升千倍以上。(3)铜-铜触点间以分子尺度融合,取消了焊料连接,因此避免了与焊料相关的问题,实现键合可靠性的提高。

1.3WLP、2.5D、3D是当前主流的几种先进封装

晶圆级封装(WaferLevelChipScalePackaging,WLP)

WLP指在晶圆前道工序完成后,直接对晶圆进行封装,再切割分离成单一芯片,WLP封装后的芯片尺寸和裸芯片几乎一致,符合消费类电子产品轻、小、短、薄化的市场趋势,且具有低成本、散热佳等优点。WLP有Fan-in(扇入式)和Fan-Out(扇出式)两种类型。FIWLP(Fan-inWLP)尺寸与芯片本身尺寸相同,不足是I/O数量一般较少。FOWLP(Fan-OutWLP)实现在芯片面积范围外充分利用RDL做连接,相比同面积的FIWLP,FOWLP拥有更多引脚数。

2.5D封装

2.5D封装有两种类型。一种是通过中介层实现芯片和基板的连接,先在中介层上层封装芯片、再将中介层封装在封装基板上的一种封装工艺,中介层是一块拥有TSV和RDL布线的晶圆,典型代表是台积电的CoWoS。另一种是通过“桥”在相邻芯片之间建立连接,首先用具有高I/O密度的硅块作为“桥梁”,其次将“桥”嵌入封装基板的空腔内,典型代表是英特尔的EMIB封装。

3D封装

3D封装指通过TSV技术,实现多个芯片垂直堆叠并互连。3D封装中,芯片相互靠得很近,所以延迟会更少,此外互连长度的缩短,能减少相关寄生效应,使器件以更高的频率运行,从而转化为性能改进,并更大程度的降低成本。HBM中的内存堆叠、HMC、3DNANDStack、3DFabric、FoverosDirect等属于3D封装。

2.先进封装大势所趋,2028年全球市场规模有望785.5亿美元

2.1摩尔定律面临瓶颈,先进封装大势所趋

摩尔定律指引过去五十多年全球半导体行业的发展。摩尔定律(Moore’sLaw)由时任仙童半导体研发总监的戈登·摩尔于1965提出,半导体芯片上集成的晶体管和电阻数量将每年增加一倍。1975年,摩尔当时的同事,英特尔高管大卫·豪斯将摩尔定律进一步完善为:在功耗不增加的前提下,每隔18个月集成电路单位面积内晶体数量翻倍。过去五十多年,半导体芯片上集成的晶体管数量基本沿着摩尔定律在增加。产业界主要通过工艺制程的创新将越来越多的晶体管整合到更小的芯片上,1970年半导体加工制程约为10μm,2022年台积电3nm制程已经实现量产。

摩尔定律面临放缓和瓶颈。自2008年45nm节点以来,台积电只能做到每隔3年让AMD的CPU内核晶体管密度翻倍,能效要每隔3.6年才能实现翻倍。摩尔定律主要面临以下瓶颈:(1)芯片内单个晶体管大小逼近原子极限,硅芯片将达到物理极限(原子尺直径约为0.1nm,1nm的晶体管沟道长度不到10个硅原子);(2)漏电流,当栅极(Gate)的宽度小于5nm时,将会产生隧道效应,电子会自行穿越通道,从而造成“0”、“1”逻辑错误;(3)功耗和散热,单位面积的功耗会由于晶体管集成度提高而提高,温度太高影响晶体管性能;(4)成本,5nm制程的芯片设计需要超过5亿美元成本,制造成本更高。

先进封装是超越摩尔定律、提升芯片性能的关键。随着硅芯片将达到物理极限,通过缩小晶体管实现芯片性能提升成本越来越高,以芯粒异质集成为核心的先进封装技术,成为了集成电路发展的关键路径和突破口。相比传统封装,先进封装具有小型化、轻薄化、高密度、低功耗和功能融合等优点,不仅可以提升性能、拓展功能、优化形态、降低成本。目前最有代表性且已经实现大规模量产的先进封装是采用TSMCCoWoS(Chip-on-Wafer-on-Substrate)封装形式的英伟达GPU芯片。

2.22028年全球市场规模有望785.5亿美元,通信基础设施领域增长最快

2028年全球市场规模有望785.5亿美元。先进封装技术的应用范围广泛,涵盖了移动设备、高性能计算、物联网等多个领域。现代智能手机中大量使用了CSP和3D封装技术,以实现高性能、低功耗和小尺寸的目标;在高性能计算领域,2.5D和3D集成技术被广泛应用于处理器和存储器的封装,显著提升了计算性能和数据传输效率。Yole预计,全球先进封装市场规模有望从2023年的468.3亿美元增长到2028年的785.5亿美元。先进封装占封装市场比例预计由2022年的46.6%提升至2028年的54.8%。

下游手机消费市场占比最大,通信基础设施领域增长最快。Yole预计,未来手机消费领域仍是先进封装最大的市场,2028年预计占比61%,不过相较2022年的70%有所下降。通信基础设施领域和汽车领域占比有所提升,2028年预计分别达到27%和9%。从增速看,通信基础设施是先进封装增长最快的领域,2022-2028年预计实现17%的复合增长。

2.3算力时代,先进封装有望迎来加速发展

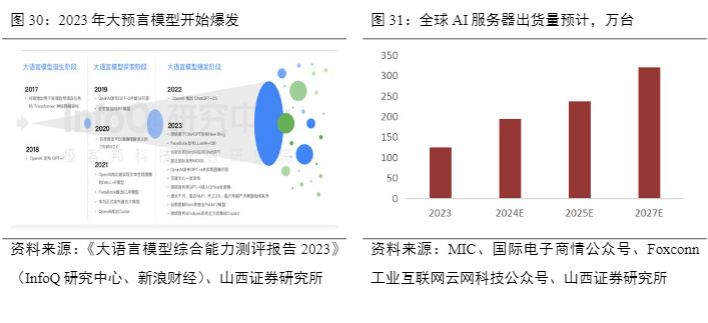

生成式AI热潮持续带动全球AI服务器出货成长。各大云端服务商正竞相布局大型语言模型(LLM)和生成式AI应用,如OpenAI的ChatGPT、Google推出Gemini、Amazon在训练新的LLM,以及国内各大厂商的大模型。LLM和生成式AI应用的大发展带动了全球AI服务器的需求,MIC预估,2024年全球AI服务器出货量为194.2万台,且将一路成长至2027年320.6万台,2022-2027年间年复合成长率(CAGR)为24.7%,其中包含价格昂贵并采用高端GPU的AI训练服务器,以及采用中低端GPU、FPGA、ASIC的AI推理服务器。

算力时代,先进封装有望迎来加速发展。先进封装可以突破带宽瓶颈,提升芯片性能。存储器的“存储墙”限制了计算芯片性能的发挥,GDDR5的带宽极限为32GB/s。由逻辑芯片和多层DRAM堆叠而成的HBM技术可以突破带宽瓶颈,HBM1和HBM2的带宽分别为128GB/s和256GB/s,HBM3可突破1.075TB/s。通过先进封装,如台积电CoWoS技术,将HBM和处理器集成,可以显著提升芯片性能。英伟达从2020年开始采用台积电CoWoS技术封装其A100GPU系列产品。随着AI及HPC等高算力芯片对先进封装技术的需求日益提升,先进封装行业有望迎来加速发展。

3.产业链梳理

3.1封装环节:Foundry与OSAT各有侧重,内资厂商积极布局先进封装

Top10厂商先进封装份额89%,封测厂与晶圆代工厂各有侧重。当前,OSAT、Foundry、IDM厂商都在大力发展先进封装。Yole数据显示,2022年日月光、安靠和台积电分别以25.0%、12.4%、12.3%份额位居先进封装市场前三;Top5厂商市占率67.9%,Top10厂商份额达到89%,行业高度集中。从厂商类型看,OSAT、Foundry、IDM分别占有65.1%、12.3%、22.6%份额。IDM、Foundry由于在前道环节经验更丰富,能更快掌握需要蚀刻等前道步骤的TSV技术,在2.5D/3D封装、混合键合等技术方面较为领先;OSAT更熟悉后道环节、异质异构集成,因此在SiP、WLP等技术相对有优势。

中国大陆厂商中,长电科技、通富微电、华天科技在先进封装领域相对领先,晶方科技、甬矽电子、颀中科技、汇成股份等公司亦积极布局。

长电科技,公司在WLP、2.5D/3D、系统级(SiP)封装技术方面均有布局。在高性能先进封装领域,公司推出的XDFOI®Chiplet高密度多维异构集成系列工艺已按计划进入稳定量产阶段,该技术涵盖2D、2.5D、3D集成技术。子公司长电微电子晶圆级微系统集成高端制造项目,计划2024H1开始设备进场。该项目聚焦全球领先的2.5D/3D高密度晶圆级封装,面向全球高性能、高算力市场。

通富微电,公司在Chiplet、2D+等封装技术方面均有储备。截至2023年12月31日,公司累计国内外专利申请达1544件,先进封装技术布局占比超六成。超大尺寸2D+封装技术、3维堆叠封装技术、大尺寸多芯片chiplast封装技术已通过客户验证。

华天科技,公司持续开展先进封装技术和工艺研发,推进FOPLP封装工艺开发和2.5D工艺验证,通过汽车级AECQ100Grade0封装工艺验证,具备3DNANDFlash32层超薄芯片堆叠封装能力。

晶方科技,公司是全球将WLCSP专注应用在以影像传感器为代表的传感器领域的先行者与引领者,同时拥有领先的硅通孔(TSV)、WLP、Fanout等封装技术。

甬矽电子,公司通过实施Bumping项目掌握了RDL及凸点加工能力,并积极布局扇出式封装(Fan-out)及2.5D/3D封装工艺。

本文仅供参考,不代表我们的任何投资建议。如需使用相关信息,请参阅报告原文。