2023中国半导体ip行业研究报告

2023中国半导体IP行业研究报告

摩尔定律:由 Gordon Moore 在1965年提出,指集成电路特征尺寸随时间按照指数规律缩小的法则。具体可归纳为:集成电路芯片上所集成的电路数目,大约每隔18 -

24个月就翻一番。在半导体行业发展的前 50 年,真实晶体管的密度发展规律基本遵循摩尔定律。

◆ IDM: 半导体垂直整合型公司(Integrated Device Manufacture,IDM),指从设计、制造、封装测试到销售自有品牌IC都一手包办的半导体垂直整合型公司。

◆ Foundry:晶圆代工厂,在集成电路领域是指专门负责生产、制造芯片的厂家。

◆ Fabless: Fabrication(制造)和less(无、没有)的组合,是指“没有制造业务、只专注于设计”的集成电路设计的一种运作模式,也用来指代未拥有芯片制造工厂的IC 设计公司。

◆ OSAT:外包半导体(产品)封装和测试(Outsourced Semiconductor Assembly and Testing,OSAT)。为一些Foundry公司做芯片产品封装和测试的产业链环节。

◆ EDA:电子设计自动化(Electronic design automation,EDA),是指利用计算机辅助设计(CAD)软件,来完成超大规模集成电路芯片的功能设计、综合、验证、物

理设计(包括布局、布线、版图、设计规则检查等)等流程的设计方式。

◆ chiplet:芯粒,是一种功能电路块,Chiplet技术就是将一个功能丰富且面积较大的芯片裸片(die)拆分成多个芯粒(chiplet),并将这些具有特定功能的芯粒通过先进 封装的形式组合在一起,最终形成一个系统芯片。

◆ RISC-V:基于精简指令集计算(Reduced Instruction Set Computer,RISC)原理建立的开放指令集架构(ISA),RISC-V是在指令集不断发展和成熟的基础上建立的全新 指令。

◆ PPA:Performance(性能)、Power(功耗)、Area(尺寸)的缩写,是芯片设计中最重要的三大要素。

◆ 异构计算:Heterogeneous Computing,指使用不同类型指令集和体系架构的计算单元组成系统的计算方式。

◆ MCM:多芯片组件,将多块半导体裸芯片组装在一块布线基板上的一种IC封装技术。

◆ Interposer:硅中介层,指在高速运行的高性能芯片和低速运行的PCB板之间插入的微电路板。

◆ TSMC CoWos:台积电(TSMC)的CoWoS(Chip-on-Wafer-on-Substrate),是一项2.5D封装技术,可以将多个小芯片封装到一个基板上。

◆ FOWLP:扇出型晶圆级封装( Fan-out Wafer Level Packaging,FOWLP),无需使用中介层或硅通孔,即可实现外形尺寸更小芯片的封装异构集成。

◆ TSMC InFO WLP:台积电的集成扇出型晶圆级封装(Integrated Fan-Out Wafer Level Packaging ),在单一封装中具有更好的电气特性,保证电气元件更高的集成度。

◆ Samsung FOPLP:三星的面板级扇出型封装(Fan-Out Panel Level Packaging,FOPLP)技术,将晶圆上的芯片切割好后,再置于方型载板中进行封装。

中国半导体IP行业发展概况

1.1 概念定义与研究范围

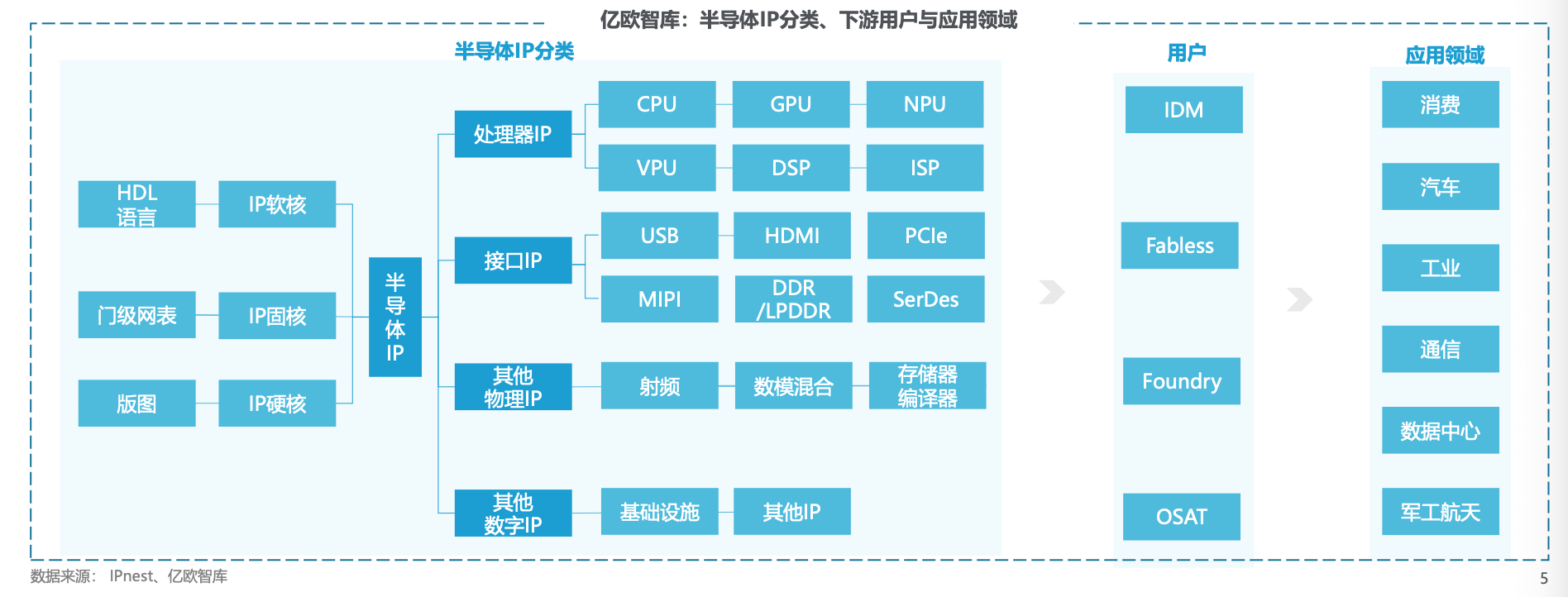

半导体IP (Intellectual Property,知识产权):通常也称作IP核(IP core),指芯片设计中预先设计、验证好的功能模块,处于半导体产业

链最上游,为芯片设计厂商提供设计模块。

◆ 半导体IP按交付方式可分为软核、硬核和固核;按产品类型可分为处理器IP、接口IP、其他物理IP及其他数字IP。由于其他数字IP无专门厂商,

本报告主要对前三类半导体IP进行细分分析。

◆ 随着半导体行业高度垂直分化发展,半导体IP的用户可分为IDM、晶圆代工厂、Fabless及OSAT四大类型,并广泛落地应用于消费、通信、汽车、

工业、军工航天及数据中心等细分领域。

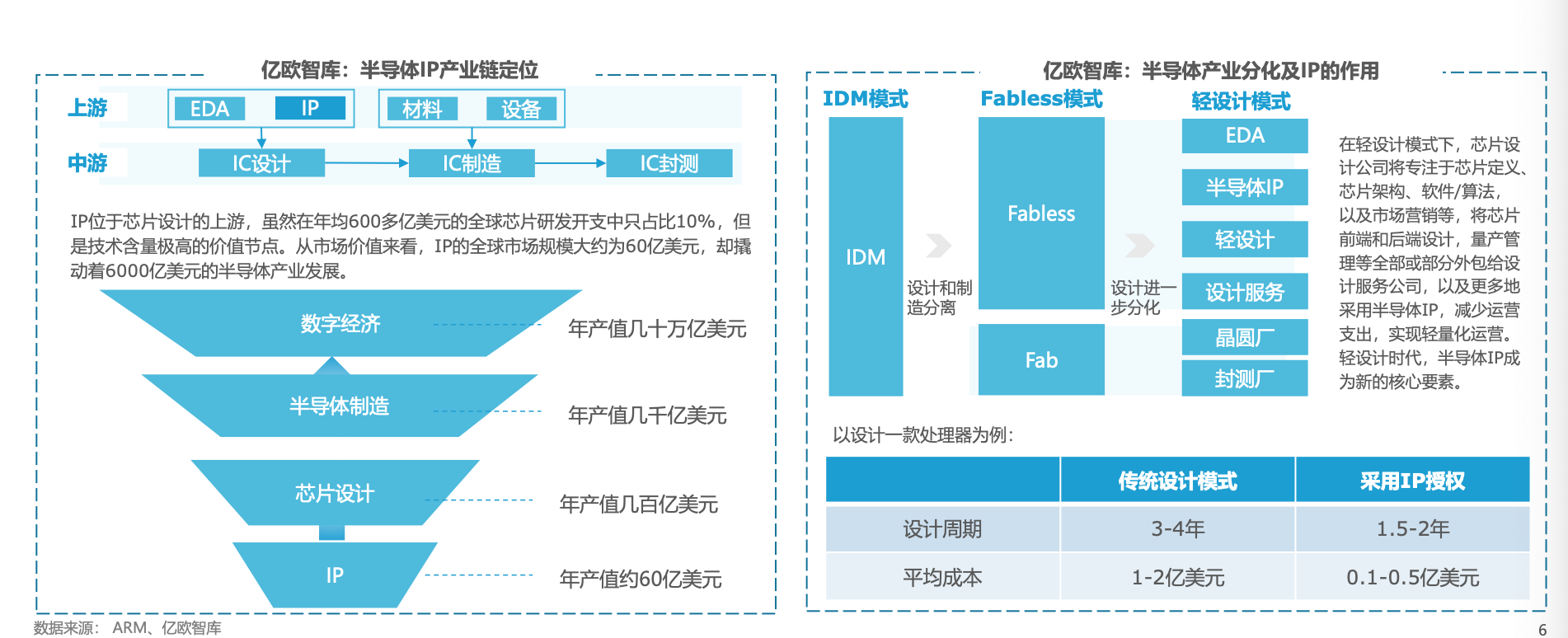

1.2 行业定位:半导体上游产业链的关键环节,产业高度垂直分化发展的必然结果

半导体IP处于半导体上游供应环节,由于性能高、设计复杂、功耗优、成本适中、技术密集度高、知识产权集中、商业价值昂贵,已经逐渐成为芯 片设计的核心产业要素和竞争力体现。

◆ IP行业是半导体产业分工精细化的结果。轻设计时代,设计公司通过购买成熟可靠的IP方案,就可以实现某个特定功能。这不仅大大降低了芯片设 计的难度与成本,还以可复用的模式形成风险共担、利益共享的生态圈,使得用户能专注自身优势价值的创新性,令低成本创新成为可能。

1.3.1 行业驱力:先进制程迭代,芯片设计成本提升,愈加催生IP需求

摩尔定律下,随着先进制程不断演进及线宽的缩小,芯片中晶体管数量大幅提升,以解决更复杂的功能应用,而复杂的功能应用对IP的数量和性能 需求不断快速提升。

◆ 先进工艺节点在提高芯片单位面积性能、降低单位成本的同时,也大幅提升了芯片的设计成本和设计风险。为此,芯片设计公司出于降低成本、平 摊风险与加速产品上市的考量,更多地使用经过验证的半导体IP。

1.3.2 行业驱力:下游市场主导力量更替,数据中心、汽车、AI等为产业带来新增量

虽然当前半导体产业处于下行周期,但产业本身已进入了继个人电脑和智能手机后的下一个发展周期。下游市场中,在消费终端市场疲软、消费电 子类芯片库存堆积的同时,数据中心、汽车、 AI、工业等领域的芯片供不应求。

◆ 其中,受新基建、数字化转型与数字中国远景目标等国家政策促进及企业将本增效需求驱动,我国数据中心业务持续高速增长,近三年年均复合增 长率达到30.69%,而这需要各式芯片来处理庞大数据;汽车作为IP下游主要应用领域之一,中国汽车智能化趋势将为半导体IP行业在内的汽车产 业链各环节带来增量;此外,人工智能的拓展应用也不断催生AI芯片的需求,而AI芯片市场的快速发展也离不开新的相关AI IP核的支撑。

1.4 行业格局:大者恒大,小者独存,IP完备度与生态能力成核心竞争要素

◆ IP行业于90年代开始快速发展,行业主要玩家几经更迭,现格局市场竞争格局渐稳,行业高度集中,CR3与CR10分别高达66.2%和79.3%。但 由于IP核的定制化特性,规模小的公司获得部分细分市场的核心知识产权及应用后,快马加鞭也能在市场占得一席之地,保证其正常的运营能力和 持续的盈利能力。

◆ 因此,亿欧智库从IP完备度、生态能力及差异化特性三大指标来评估IP厂商。其中,IP完备度越高、生态能力越强,则厂商竞争能力越强;但后发 者可以通过聚焦某一细分领域来抓住差异化特性,从而获得竞争优势,后来居上。

02 中国半导体IP行业细分领域分析

2.1 半导体IP衡量要素:技术、量产、服务及抗风险四大指标构筑IP竞争力

除去衡量IP厂商的IP完备度、生态能力及差异化特性外,半导体IP衡量要素还涉及四大分析维度:技术能力、量产能力、服务能力及抗风险能力; 以及PPA、协议、自研、工艺、产品组合、验证、专业团队、产品生命周期管理、定制化、风险等12个细分指标。

◆ 由于国产IP产品品类较少且分布不均,竞争格局尚不明朗,难以进行细化指标评估。总体而言,当前国产IP在自主可控、技术水平、工艺节点覆盖 能力、行业标准等方面与国际厂商相比较弱,随着国产化需求推动、背靠本土广阔市场等优势,以及人才水平、技术水平提升,国产IP的发展仍有 广阔空间。

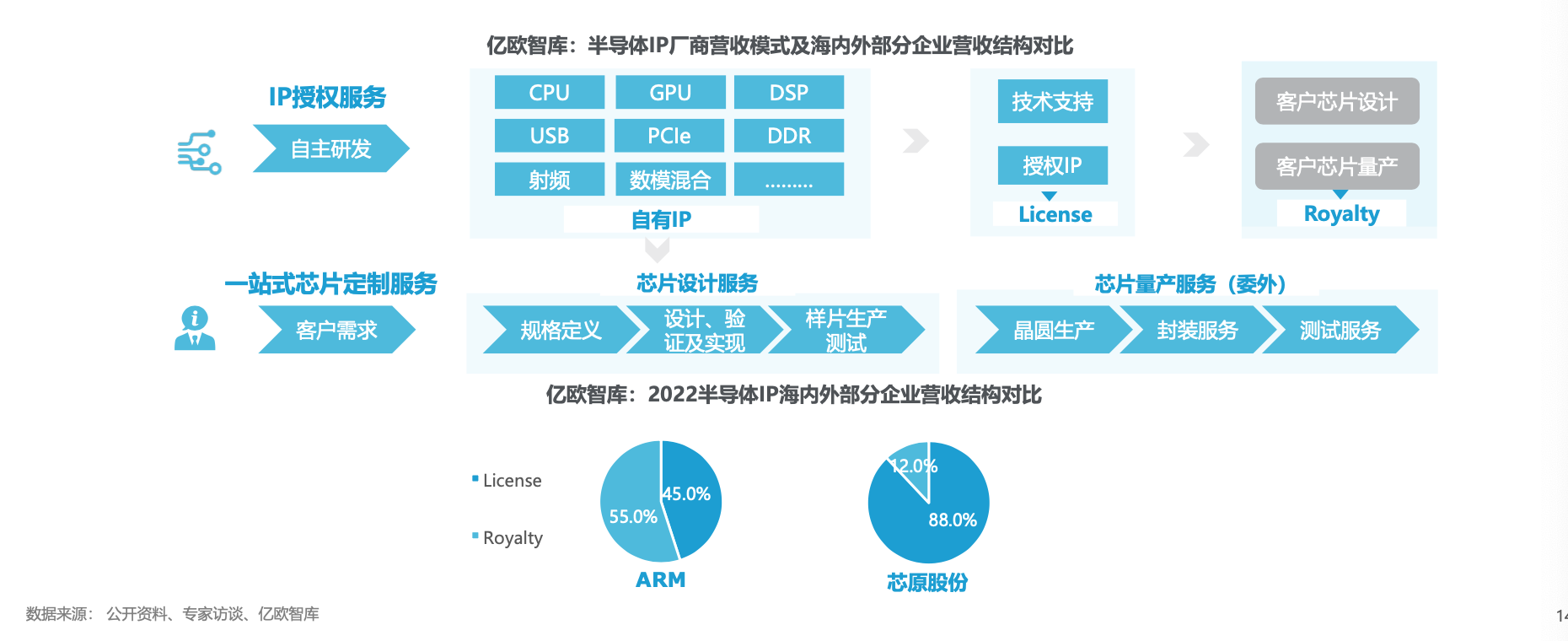

2.2 半导体IP:营收模式成熟,海外以版税为主,国内以授权为主

IP营收模式为前期授权(License)与后期版税(Royalty),前者是将集成电路设计时所需用到的经过验证、可重复使用且具备特定功能的模块 (即半导体IP)授权给客户使用,并提供相应的配套软件与技术支持。后者为向客户交付IP时进行一次性收费,为客户完成芯片量产和销售后按费 率产生收入,版税收入将依赖于客户搭载IP产品的销量。海外龙头公司均采用收取IP授权费与版税的营收模式,国内半导体IP公司除了采取类似的 收入模式外,还基于独立设计IP提供芯片定制服务。

◆ 海外龙头公司业务模式成熟、客户稳定,其业务收入主要来源于版税;而国内IP厂商尤其是新兴厂商,进入市场晚,业务收入仍以授权费为主。